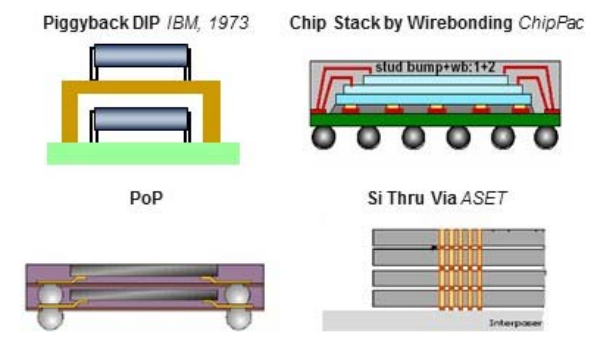

(論文[1]のFigure 1より引用)

3Dパッケージングは、メモリパッケージのパッケージングのために1970年代に始まりました。 メモリ密度は、常に2つのパスにつながる高性能コンピューティングシステムのボトルネックでした。

2Dのチップ内のメモリ密度を増やし、3Dでパッケージ化されたチップまたはベアチップの多くをスタックすることで増加します。 ただし、システムパフォーマンスの障壁は、ロジックとメモリ間の遅延と帯域幅です。ロジックとメモリの3Dスタックは、10年の究極のソリューションと見なされてきましたが、独自の障壁があります。これらの障壁は多くのアプローチで克服されていますが、究極の目標は、最小のコストで最高のパフォーマンスと信頼性を備えた小型システムを形成することです。

本論文では、ジョージア工科大学のラオ・R・タマラ氏が、デバイスレベルの3D構造のICチップとは対照的に、システムレベルで帯域幅とその他の要件の両方に対処するための3Dシステムパッケージアーキテクチャを紹介し、その研究成果を2017年度のIEEE International Electron Devices Meeting (IEDM) にて報告しています。

論文中に記載がありますが、ジョージア工科大学では、ガラス基板の上下にメモリなどの半導体を接続するアーキテクチャを提案しており、シリコン基板で実施しているTSV(Through Silicon Via)と呼ばれる貫通ビアの形状に似た、数μmの貫通ビアを形成してガラス基板越しで接続する構造を形成しています。

このことにより相互接続による速度遅延がなく、I/O密度の向上と帯域幅の確保が実現できるそうです。

URL : https://ieeexplore.ieee.org/document/8268319